Auf dem North American Technology Symposium von TSMC am Mittwoch erläuterte das Unternehmen seine Roadmaps für Halbleitertechnologie und Chip-Packaging-Technologie. Während Ersteres für die Aufrechterhaltung des traditionellen Teils des Mooreschen Gesetzes unerlässlich ist, könnte Letzteres den Trend zu Prozessoren beschleunigen, die aus immer mehr Silizium bestehen, was schnell zu Systemen in Wafergröße führt. Ein solches System, Teslas Dojo-Trainingskachel der nächsten Generation, ist laut TSMC bereits in Produktion. Und im Jahr 2027 plant die Gießerei, Technologie für Systeme im Wafer-Maßstab zu liefern, die komplexer sind als die von Tesla und die 40-mal mehr Rechenleistung als aktuelle Systeme bieten könnten.

Seit Jahrzehnten erhöhen Chiphersteller die Logikdichte auf Prozessoren, vor allem durch die Reduzierung der von Transistoren eingenommenen Fläche und der Größe der Verbindungen. Doch diesem Projekt geht schon seit einiger Zeit die Puste aus. Stattdessen setzt die Industrie auf fortschrittliche Verpackungstechnologie, die es ermöglicht, einen einzelnen Prozessor aus einer größeren Menge Silizium herzustellen. Die Größe eines einzelnen Chips wird durch die größte herstellbare Musterlithographieausrüstung begrenzt. Die sogenannte Absehengrenze liegt derzeit bei etwa 800 Quadratmillimetern. Wenn Sie also mehr Silizium in Ihrer GPU wünschen, müssen Sie sie aus zwei oder mehr Chips herstellen. Der Schlüssel besteht darin, diese Chips so zu verbinden, dass Signale so schnell und mit so wenig Energie von einem zum anderen übertragen werden können, als wären sie ein einziges großes Stück Silizium.

TSMC stellt bereits einen KI-Beschleuniger in Wafergröße für Cerebras her, aber diese Anordnung scheint einzigartig und unterscheidet sich von dem, was TSMC jetzt mit dem sogenannten System-on-Wafer anbietet.

Bis 2027 werden Sie von der vollständigen Wafer-Integration profitieren können, die 40-mal mehr Rechenleistung, mehr als 40 Silizium-Retikel und Platz für mehr als 60 Speicherchips mit hoher Bandbreite bietet, prognostiziert TSMC.

Für Cerebras stellt TSMC einen Wafer her, der mit identischen Arrays von KI-Kernen gefüllt ist, die kleiner als die Fadenkreuzgrenze sind. Es verbindet diese Netzwerke über „Trace-Linien“, die Bereiche zwischen Chips, die normalerweise leer bleiben, damit der Wafer in Chips geschnitten werden kann. Kein Chip-Herstellungsprozess ist perfekt, daher gibt es auf jedem Wafer immer fehlerhafte Teile. Aber Cerebras hat so viel Redundanz entwickelt, dass es für den fertigen Computer keine Rolle spielen würde.

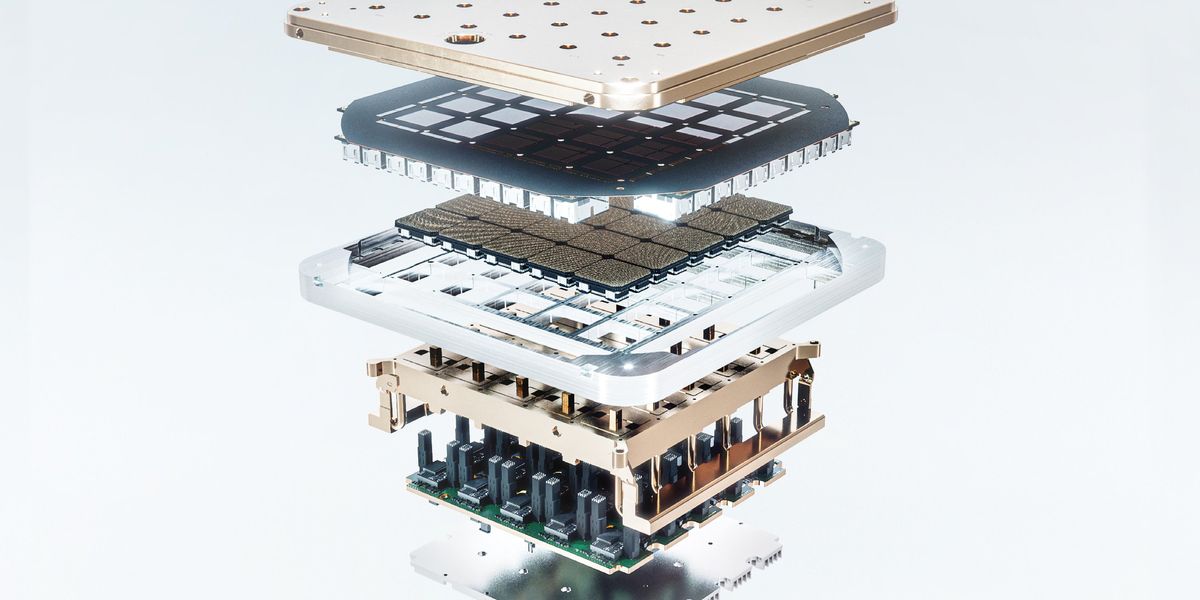

Mit seiner ersten System-on-Wafer-Serie bietet TSMC jedoch eine andere Lösung für die Probleme mit der Absehenbegrenzung und der Leistung. Es beginnt mit bereits getesteten Logikmatrizen, um Fehler zu minimieren. (Teslas Dojo enthält ein 5 x 5-Raster vorab getesteter Prozessoren.) Diese werden auf einem Trägerwafer platziert und die leeren Räume zwischen den Chips werden gefüllt. Als nächstes wird eine Verbindungsschicht mit hoher Dichte aufgebaut, um die Logik mithilfe des integrierten Prozessors von TSMC zu verbinden. Rundfunktechnik. Ziel ist es, die Datenbandbreite zwischen den Chips so hoch zu machen, dass sie praktisch wie ein großer Chip wirken.

Bis 2027 plant TSMC, eine Integration im Wafermaßstab auf Basis seiner fortschrittlicheren Chip-on-Wafer-on-Substrat (CoWoS)-Verpackungstechnologie anzubieten. Bei dieser Technologie werden vorab getestete Logik und vor allem Speicher mit hoher Bandbreite auf einem Siliziumsubstrat befestigt, das mit hochdichten Verbindungen strukturiert und von vertikalen Verbindungen, sogenannten Through-Silicon-Vias, durchquert wird. Vernetzte Logikchips können auch die Vorteile der 3D-Chiptechnologie des Unternehmens nutzen, die als System-on-Integration-Chips (SoIC) bezeichnet wird.

Die Waferscale-Version von CoWoS ist der logische Endpunkt einer Erweiterung der Verpackungstechnologie, die bereits bei High-End-GPUs zu beobachten ist. Nvidias kommende GPU Blackwell verwendet CoWos, um über drei Silizium-Retikelgrößen zu integrieren, darunter acht High-Bandwidth-Memory-Chips (HBM). Bis 2026 will das Unternehmen diese Zahl auf 5,5 Absehen, darunter 12 HBMs, erweitern. Laut TSMC würde dies zu mehr als dem 3,5-fachen der durch seine Technologie im Jahr 2023 ermöglichten Rechenleistung führen. Im Jahr 2027 werden Sie jedoch von der vollständigen Wafer-Integration profitieren können, die 40-mal mehr Rechenleistung, mehr als 40 Silizium-Retikel und Platz für mehr als 60 bietet HBMs, prognostiziert TSMC.

Wozu dient die Waferwaage?

Die 2027-Version des System-on-Wafer weist eine gewisse Ähnlichkeit mit der Technologie namens Silicon-Interconnect Fabric (Si-IF) auf, die vor mehr als fünf Jahren an der UCLA entwickelt wurde. Zum Team hinter SiIF gehören der Professor für Elektro- und Computertechnik Puneet Gupta und der IEEE-Fellow Subramanian Iyer, der nun für die Umsetzung des Verpackungsteils des US-amerikanischen CHIPS Act verantwortlich ist.

Seitdem arbeiten sie daran, die Verbindungen auf dem Wafer dichter zu machen und die Technologie um weitere Funktionen zu erweitern. „Wenn man daraus eine vollständige Technologie-Infrastruktur machen will, muss sie noch viel mehr leisten als nur eine schrittweise Konnektivität bereitzustellen“, sagt Gupta, ebenfalls IEEE-Mitglied. „Eines der größten Probleme dieser Großanlagen wird die Energieversorgung sein.“ Deshalb arbeitet das UCLA-Team an Möglichkeiten, dem Siliziumsubstrat hochwertige Kondensatoren und Induktivitäten hinzuzufügen und Galliumnitrid-Leistungstransistoren zu integrieren.

KI-Training ist die erste offensichtliche Anwendung der Technologie auf Ausschnittsebene, aber es ist nicht die einzige und möglicherweise nicht einmal die beste, sagt der Architekt Rakesh Kumar Computer Science von Urbana-Champaign an der University of Illinois und Mitglied von das IEEE. Auf dem International Computer Architecture Symposium im Juni präsentiert sein Team ein Slice-Scale-Netzwerk-Switch-Design für Rechenzentren. Ein solches System könnte die Anzahl fortschrittlicher Netzwerk-Switches in einem sehr großen Rechenzentrum (16.000 Racks) von 4.608 auf nur 48 reduzieren, berichten die Forscher. Ein viel kleineres Rechenzentrum im Unternehmensmaßstab mit beispielsweise 8.000 Servern könnte mit einem einzigen Slice-Scale-Switch betrieben werden.

Aus den Artikeln auf Ihrer Website

Verwandte Artikel im Internet